XJAnalyser jest wizualnym narzędziem służącym do analizowania oraz debugowania urządzeń w łańcuchu JTAG. Dzięki prostej, trzykrokowej konfiguracji umożliwia on natychmiastową weryfikację łańcucha po czym dostarcza interaktywny, graficzny wgląd na piny urządzeń JTAG. Dla łatwiejszej kontroli możesz grupować piny w magistrale oraz błyskawicznie generować sygnały sterujące aby śledzić połączenia w obrębie układu – użyteczne podczas weryfikacji przerw i zwarć.

Dodatkowo XJAnalyser wspiera standardy programowania urządzeń JTAG w systemie, tj. STAPL/JAM oraz SVF.

Właściwości

- Testowanie układów z obudową BGA

- Do rozpoczęcia debugowania układu wymagane są jedynie pliki BSDL

- Zmiana stanu pinów na wysoki, niski lub cykliczny

- Szybkie wyszukiwanie pinów oraz śledzenie zmiany ich wartości w czasie rzeczywistym

- Przejrzyste wyświetlanie pinów, ich numerów, nazw oraz stanów

- View JTAG chain data as waveforms

- Łączenie pinów w szyny

- Możliwość programowania układów plikami SVF iSTAPL

- Konfiguracja typu Plug and Play

- Interakcja w czasie rzeczywistym

Graficzne debugowanie sieci

Podczas śledzenia sieci połączeń układu za pomocą oscyloskopu, ustaw wartość jednego z pinów i przełącz się, aby wychwycić sygnał w różnych punktach sieci. Niezwłocznie po przesunięciu na inny pin dowiesz się, że interesujący sygnał nie jest już dłużej śledzony.

Szybko lokalizuj sygnały, które są wysyłane przez ciebie do urządzenia.

Dla przykładu monitorując sygnały zmieniające wartość możesz nacisnąć przycisk, błyskawicznie zlokalizować oraz wyświetlić pin, do którego jest on podłączony, nawet jeżeli urządzenia w łańcuchu zawierają klika tysięcy pinów.

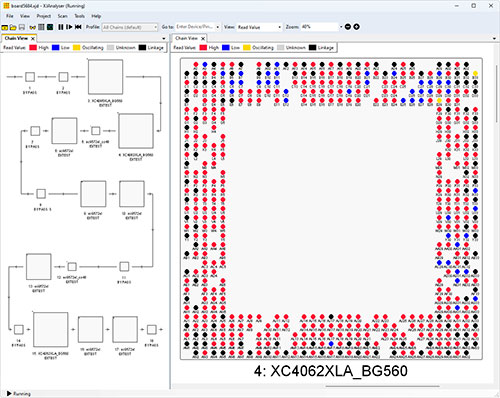

Przeglądaj interesującą sekcję łańcucha. Dla urządzeń z bardzo dużą ilością pinów, informacja z reguły może ulec zniekształceniu.

XJAnalyser rozwiązuje ten problem umożliwiając powiększenie obszaru pinów, które są dla ciebie istotne. Dozwolone jest również stosowanie kilku podglądów, przedstawiających różne, interesujące regiony łańcucha JTAG – jednocześnie.

Elastyczna kontrola

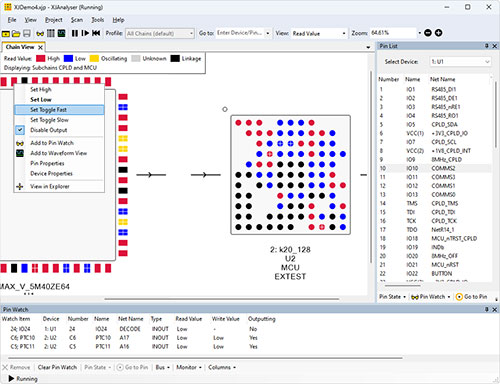

Kontroluj urządzenia w łańcuchu JTAG jedną z możliwych dróg. XJAnalyser oferuje trzy sposoby wyświetlania i sterowania pinami:

- bezpośrednia prezentacja graficzna

- tekstowa lista pinów

- podgląd wybranych pinów

W ostatnim trybie istnieje możliwość łączenia pinów w magistrale oraz zapisania ich wartości do kompletnej szyny.

Programowanie CPLD i FPGA

XJAnalyser umożliwia importowanie plików SVF oraz STAMPL/JAM, programując w ten sposób dowolny układ CPLD lub FPGA.

XJAnalyser bez problemu programuje układy w łańcuchach składających się z kilku urządzeń, nawet w przypadku, gdy pliki te zostały utworzone dla łańcucha JTAG zawierającego tylko jedno urządzenie.

Komunikacja z JTAG

Intuicyjny, graficzny interfejs zapewnia szybką komunikację z urządzeniami w łańcuchu JTAG bez konieczności programowania bądź inicjowania któregokolwiek z układów na płytce. Kontroluj stan wszystkich pinów I/O w czasie rzeczywistym oraz graficznie ustawiaj piny według wymagań w stan wysoki, niski lub cykliczny.

Upraszczaj dostęp niskiego poziomu do dowolnego urządzenia podłączonego do układu JTAG grupując piny razem w magistrale (np. „Dane” lub „Adres”) oraz ustawiaj wartości używając dogodnych jednostek w systemie szesnastkowym, binarnym lub dziesiętnym.

Unikaj uszkodzenia płytki – XJAnalyser wyświetla stosowne ostrzeżenia w momencie, gdy ustawiany przez ciebie stan dowolnego pinu może spowodować konflikt z wartością dostarczaną do sieci z innego źródła.

Trzy proste kroki

Wystarczą trzy proste kroki aby uruchomić XJAnalyser i rozpocząć wstępne debugowanie i testowanie płytki.

- Krok pierwszy: podłączenie i odpowiednie skonfigurowanie złączki JTAG

- Krok drugi: importowanie plików BSDL

- Krok trzeci: uruchomienie analizatora.

W ostanim trybie isnieje mozliwość łączenia pinów w szyny i przypisanie im wartości.

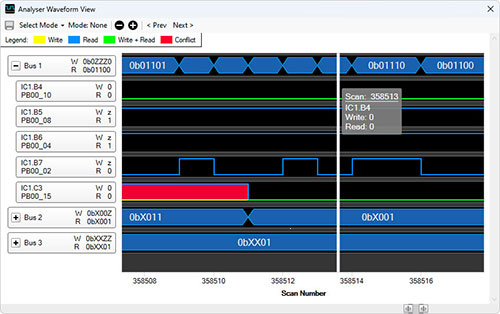

Waveform Viewer

The Waveform Viewer captures and displays the digital signal levels and transitions of JTAG chain data.

It supports triggering, allowing circuit behaviour to be captured under specified conditions, such as when particular events occur. This can greatly improve an engineering team’s ability to capture key information and track down intermittent faults.

Konfiguracja typu Plug and Play

When the machine running XJAnalyser is connected to a circuit, it automatically investigates the JTAG chain and identifies the correct BSDL files from its library, ready to run tests.

Recommended system requirements

- Intel® Core i3, i5, i7 processor or equivalent (any generation)

- Microsoft® Windows® 10 1607 and later (32 or 64 bit), or Windows 11

- 8 GB of RAM

- Real-time, pin-by-pin control of BGA and fine-pitch devices

- In-system programming using SVF/STAPL/JAM files

- Easy 4-step setup wizard

Kluczowe Korzyści

- Sterowanie wartościami pinów oraz śledzenie sygnałów, nawet dla układów BGA

- Skrócenie czasu tworzenia projektu od momentu prototypu do końcowej produkcji

- Oszczędność budżetu poprzez wyeliminowanie konieczności stosowania różnorodnych narzędzi do programowania urządzeń

Wygodne opcje licencjonowania

- Ruchoma licencja

– w sterowniku JTAG, która pozwala na instalację na dowolnej ilości komputerów - Network licence

– held on a networked license server available from anywhere in the world

For support, or for a quote on any part of the XJTAG system, please contact us.