JTAG to wiecej, niz debugowanie i programowanie

Moga Panstwo znac sie na JTAG, poniewaz uzywaja Panstwo narzedzia z interfejsem JTAG. Procesory czesto uzywaja interfejsów JTAG, aby zapewnic dostep do ich funkcji debugowania bramek FPGA (Field-Programmable Gate Arrays) oraz zlozonych uklady elektroniczne CPLD (Complex Programmable Logic Devices) wykorzystujac JTAG w celu zapewnienia dostepu do ich funkcji programowania.

JTAG jest NIE TYLKO technologia do debugowania/emulacji procesora.

JTAG jest NIE TYLKO technologia do programowania zlozonych programowalnych ukladów elektronicznych.

Narzedzia debugowania i programowania powszechnie zwiazane z JTAG wykorzystuja tylko jeden aspekt podstawowej technologii – 4-przewodowy protokól komunikacyjny JTAG.

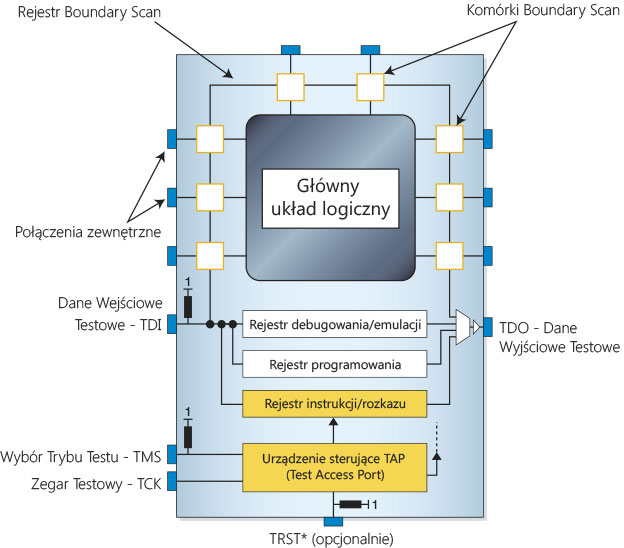

Te cztery sygnaly, znane pod wspólna nazwa jako Test Access Port (testowy port dostepu) albo TAP, sa czescia standardu IEEE 1149.1. Standard ten zostal opracowany w celu dostarczenia technologii do testowania zespolów plytek obwodów drukowanych (PCBA) bez koniecznosci fizycznego dostepu do poziomu wymaganego dla testowania loza fakira (z wystajacymi szpilkami) lub ilosci dopasowanej do potrzeb klienta (opracowywanej na zlecenie uzytkownika) potrzebnej do testu funkcjonalnego. TAP zostal zaprojektowany do wspóldzialania z nowymi rejestrami, które zostaly dodane do urzadzen do wdrozenia tej metody testowania.

Jednak bardzo szybko producenci krzemu dostrzegli korzysci plynace z korzystania z TAP, aby uzyskac dostep do rejestrów oferujac inne funkcjonalnosci takie, jak debugowanie i programowanie.

Glówny rejestr dodany do urzadzenia specjalnie do testowania JTAG nazywany jest Rejestrem Boundary-Scan (BSR). Jak sama nazwa wskazuje, poszczególne bity lub komórki tego rejestru sa na granicy urzadzenia, miedzy jego rdzeniem funkcjonalnym, a pinami, poprzez które jest podlaczony do plyty (plytki drukowanej) – bardzo czesto testowanie JTAG jest okreslane, jako boundary-scan (skanowanie graniczna sciezka obserwacyjno-sterujaca).

W jaki sposób JTAG Boundary-Scan jest wykorzystywany do testowania plytki drukowanej

Komórki Boundary-Scan (patrz powyzej) moga pracowac w dwóch trybach. W ich trybie funkcjonalnym nie maja zadnego wplywu na dzialanie urzadzenia – jest to tryb, w którym dzialaja, gdy plytka drukowana pracuje normalnie. W ich trybie testowym odlaczaja rdzen funkcjonalny urzadzenia od pinów. Poprzez umieszczenie komórek boundary-scan w trybie testowym moga byc one wykorzystane do kontroli wartosci sterowanych z wlaczonego urzadzenia do sieci, a takze moga byc wykorzystywane do monitorowania wartosci tej sieci.

Odlaczenie sterowania pinów od funkcji wlaczonego urzadzenia sprawia, ze rozwój testu boundary-scan jest znacznie latwiejszy od tradycyjnego testu funkcjonalnego, poniewaz do uzywania pinów nie jest wymagane zadna konfiguracja urzadzenia albo rozruch. Przez dostarczenie mechanizmu do kontroli i monitorowania wszystkich wlaczonych/uaktywnionych sygnalów na urzadzeniu z 4-pinowego TAP, JTAG znacznie zmniejsza fizyczny dostep wymagany do przetestowania plytki dukowanej.

Istnieja dwa glówne sposoby, aby ta mozliwosc boundary-scan mogla byc wykorzystana do testowania plytki drukowanej. Pierwszy sposób, testowanie polaczenia (patrz nastepny paragraf) daje dobry zasieg testu, szczególnie dla uszkodzen zwarciowych. Jest on oparty wylacznie na mozliwosciach urzadzenia JTAG, polaczeniach i sieciach na plytce drukowanej oraz – w przypadku XJTAG – na funkcjonalnosci logiki na plytce drukowanej. Drugi sposób rozszerza ten zakres za pomoca uaktywnionych urzadzen JTAG na plytce drukowanej do komunikowania sie z urzadzeniami peryferyjnymi bez JTAG, takimi jak pamiec o dostepie bezposrednim (RAM) DDR o podwójnej szybkosci transmisji danych i pamiec flash.

Co to jest test polaczenia JTAG?

Testowanie polaczenia JTAG sprawdzi, czy polaczenia wokól urzadzen umozliwiajacych wspóldzialanie z JTAG na plytce drukowanej sa takie same, jak te okreslone w projekcie.

Tam, gdzie dwa wlaczone piny JTAG sa przeznaczone do podlaczenia, test pozwoli upewnic sie, ze jeden pin moze byc sterowany przez inny. Tam, gdzie wlaczone piny nie sa przeznaczone do podlaczenia, sa one testowane pod katem uszkodzen zwarciowych przez jeden pin prowadzacy i upewniajac sie, czy te wartosci nie sa odczytywane na innych pinach.

Dzieki testowi polaczenia, moga byc równiez znalezione brakujace rezystory podciagajace do potencjalu zasilania oraz uszkodzenia “utkniecia na”, jak równiez defekty obejmujace urzadzenia logiki, których zachowanie moze byc opisane w matrycy prawdziwosci.

XJTAG bedzie automatycznie generowac wektory wymagane do uruchomienia testu polaczenia na podstawie wykazu sieci plytki drukowanej oraz informacje JTAG dla uaktywnionych urzadzen.

Co z urzadzeniami, które nie umozliwiaja wspóldzialania z JTAG?

Podczas, gdy glówne urzadzenia takie, jak procesory oraz bezposrednio programowalne macierze bramek (FPGA), umozliwiaja zwykle wspóldzialanie z JTAG, w kazdym projekcie bedzie wiele takich urzadzen, które nie umozliwiaja takiego wspóldzialania. Pamieci DDR, SDRAM (rodzaj pamieci DRAM pracujacej synchronicznie z magistrala systemowa), SRAM (statyczna pamiec o dostepie bezposrednim), pamiec flash, zarzadzanie danymi wejsciowymi i wyjsciowymi (MDIO) sterowanymi urzadzeniami warstwy fizycznej (PHY) sieci Ethernet, SPI oraz czujniki temperatury ukladów scalonych typu I²C, zegary czasu rzeczywistego, przetworniki analogowo-cyfrowe (ADC) i przetworniki cyfrowo-analogowe (DAC), to tylko kilka przykladów takich urzadzen.

Test polaczenia bedzie nadal zapewniac doskonaly zasieg uszkodzen zwarciowych w sieciach, laczac urzadzenia bez JTAG z aktywowanymi urzadzeniami JTAG; jednakze nie moze on sprawdzac uszkodzen obwodu otwartego ani w zadnym urzadzeniu JTAG, ani tez w urzadzeniu bez JTAG.

Aby dodac ten zasieg obwodu otwartego konieczne jest komunikowanie sie z urzadzeniem peryferyjnym wg boundary-scan na aktywowanym urzadzeniu. Jesli komunikacja moze byc zweryfikowana, nie moze byc usterki obwodu otwartego. Ten rodzaj testowania moze byc bardzo prosty, na przyklad oswietlenie LED i poproszenie operatora w celu sprawdzenia, czy nie zostalo ono aktywowane lub bardziej zlozony, na przyklad zapis danych do tablicy pamieci RAM i czytanie go wsteczne.

Czy jest duzo pracy, by stworzyc system testowy JTAG?

Przy uzyciu bibliotek dla standardowych podzespolów bez JTAG dostarczanych przez XJTAG, mozna uzyskac zestaw testów i do uruchomienia na plytce drukowanej bez wywolywania kodowania. Pliki biblioteki zawieraja modele dla wszystkich typów urzadzen bez JTAG od prostych rezystorów i buforów do urzadzen o zlozonej pamieci takich, jak DDR3. Poniewaz boundary-scan rozlacza sterowanie pinów na urzadzeniach JTAG od ich funkcjonalnosci, ten sam model moze byc wykorzystywany niezaleznie od urzadzenia JTAG sterujacego urzadzeniem peryferyjnym.

Wiekszosc plytek drukowanych zawiera juz naglówki JTAG do programowania lub debugowania, wiec nie ma dodatkowych wymagan projektowych.

Gdzie moge uzyskac informacje na temat JTAG w moich urzadzeniach?

Aby uruchomic jakikolwiek boundary-scan na podstawie testowania, niezbedne jest posiadanie pewnych informacji o wdrozeniu JTAG na wlaczonych urzadzeniach na plycie (plytce drukowanej). Informacja ta pochodzi z plików BSDL (jezyka opisu Boundary-Scan) dla tych urzadzen. Pliki BSDL musza byc udostepnione przez sprzedawce podzespolów elektronicznych zastosowanych w urzadzeniu, które sa zgodne ze standardem 1149.1. IEEE.

Czy test JTAG jest dopiero co wykorzystywany w produkcji?

Wcale nie. Jedna z kluczowych zalet testowania boundary-scan jest to, ze tylko wymagany testowany sprzet komputerowy jest urzadzeniem sterujacym JTAG. Inne techniki testu produkcyjnego takie, jak sonda przemieszczajaca sie nad testowanym obiektem, zautomatyzowana inspekcja optyczna, rentgenowska lub z wykorzystaniem zespolu glowic szpilkowych w postaci macierzy sond, wszystkie wymagaja specjalistycznego oprzyrzadowania testowego, które nie beda dostepne na pulpicie inzyniera.

Wykorzystanie boundary-scan podczas obserwacji na ekranie komputera moze usunac watpliwosci inzynierów sprzetu komputerowego, którzy moga przetestowac prototypowe plytki drukowane pod katem wad produkcyjnych, jeszcze przed testowaniem produktu, oraz zanim oprogramowanie ukladowe nie jest jeszcze kompletne. Systemy testowe opracowane na tym wczesnym etapie cyklu zycia produktu moga byc latwo ponownie uzyte, oraz rozszerzone na produkcje.

Dlaczego powinienem uzywac JTAG Boundary-Scan do testowania moich plytek drukowanych?

Trzy proste litery – BGA

Coraz wieksza ilosc urzadzen dostarczana jest w opakowaniach BGA (Ball Grid Array), czyli technologii montazu powierzchniowego uzywanego dla ukladów scalonych. Kazde urzadzenie BGA na plytce drukowanej naklada powazne ograniczenia w zakresie testowania, które moze sie odbywac przy uzyciu tradycyjnych maszyn typu zespolu glowic szpilkowych w postaci macierzy sond lub sondy przemieszczajacej sie nad testowanym obiektem.

Za pomoca prostego interfejsu 4-pinowego, JTAG boundary-scan pozwala na sterowanie i monitorowanie sygnalów na aktywowanych urzadzeniach bez zadnego bezposredniego dostepu fizycznego.

Jednorazowe koszty inzynieryjne

Jednorazowe koszty inzynieryjne (NRE) konstruowania stalych testowych elementów oprzyrzadowania moga byc niewspólmiernie wysokie. W wielu przypadkach uzywajac JTAG boundary-scan wyeliminujemy potrzebe takiego oprzyrzadowania, w innych przypadkach oprzyrzadowanie testowe moze byc znacznie uproszczone przynoszac w rezultacie znaczne oszczednosci kosztów.

Krótsze czasy testowania

W przypadku plytek drukowanych o niskim wolumenie produkcji, zawsze bylo trudne uzasadnienie kosztów opracowania oprzyrzadowania testowego. W tych przypadkach jedna alternatywa jest testowanie typu “flying probe” (sondy przemieszczajacej sie nad testowanym obiektem); jednak czasy cyklu testu wydaja sie byc wysokie dla tej technologii. Test JTAG boundary-scan daje szybkie czasy testów bez koniecznosci stosowania kosztownego oprzyrzadowania.

Nizsze koszty prac rozwojowych i opracowywania testów

Poniewaz rózne procesory typu FPGA komunikuja sie z urzadzeniami peryferyjnymi na rózne sposoby, tradycyjny test funkcjonalny wymaga kosztownego dopasowania do potrzeb klienta dla kazdej plytki drukowanej. JTAG boundary-scan znacznie zmniejsza takie koszty, poniewaz zapewnia uproszczony interfejs do sterowania pinami wejscie-wyjscie sluzacymi do komunikowania sie z urzadzeniami peryferyjnymi. Ten standardowy interfejs, który jest taki sam dla wszystkich aktywowanych urzadzen JTAG, oznacza ogólny zestaw modeli testów, które moga byc stosowane i ponownie wykorzystywane przy budowie systemów testujacych.

Jedno narzedzie do testu i programowania

JTAG jest juz czesto uzywany, jako jeden krok w produkcji: w programowaniu. Uzywajac JTAG równiez dla testu boundary-scan mozliwe jest zmniejszenie liczby kroków i czynnosci dotyczacych obslugi w procesie produkcji.

Testy poziomu produkcji na stole warsztatowym/pulpicie inzyniera dla prototypowych plytek drukowanych

Tradycyjne technologie testowania wymagaja bardzo duzego i kosztownego wyposazenia. Jedynym wyposazeniem testowym wymaganym dla testowania JTAG boundary-scan jest urzadzenie sterujace JTAG – urzadzenie sterujace XJLink2 jest pod wzgledem wielkosci podobne do myszy komputera osobistego.

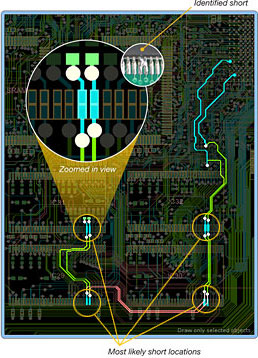

Doskonala diagnostyka usterek

JTAG boundary-scan, w przeciwienstwie do testu funkcjonalnego, zapewnia informacje o usterce o wysokiej dokladnosci, aby pomóc przy szybkiej naprawie. XJTAG zapewnia równiez mozliwosc ogladania zarówno fizycznej lokalizacji usterki na ukladzie plytki drukowanej, jak i logiczna konstrukcje obszaru obwodu, w którym usterka istnieje na schemacie.

Odzyskiwanie „martwych” plytek drukowanych tam, gdzie nie dzialalby test funkcjonalny

Testy JTAG boundary-scan moga byc uruchamiane na jakiejkolwiek plytce drukowanej z interfejsem roboczym JTAG. Tradycyjne testy funkcjonalne nie moga byc uruchamiane, jezeli plytka drukowana nie uruchamia sie; pospolite usterki na kluczowych urzadzeniach peryferyjnych, takie jak usterki pamieci RAM lub zegarów, moglyby byc znalezione za pomoca JTAG, ale uniemozliwialyby testy funkcjonalne z dostarczaniem wszelkich informacji diagnostycznych.

Inne zasoby

High-Level Guide to JTAG

See what JTAG can do

Technical Guide to JTAG

A low-level look at how JTAG is implemented

Wskazówki Design-For-Testability (DFT)

Suggestions for improving the testability of circuits

JTAG Testing with XJTAG

How XJTAG extends the possibilities of JTAG