- Neues, einfach zu bedienendes „Design for Test“ (DFT)-Tool

- Kostenlos für Nutzer von PADS-Schematic-Design

- Vermeiden Sie kostspielige Re-Spins durch Entdeckung von Fehlern bereits während der Designphase

- Finden Sie Fehler in der/den JTAG-Kette(n) und beseitigen Sie diese vor Herstellung der Hardware

- Nutzen Sie die volle Leistung von Boundary-Scan, um die Testbarkeit zu verbessern

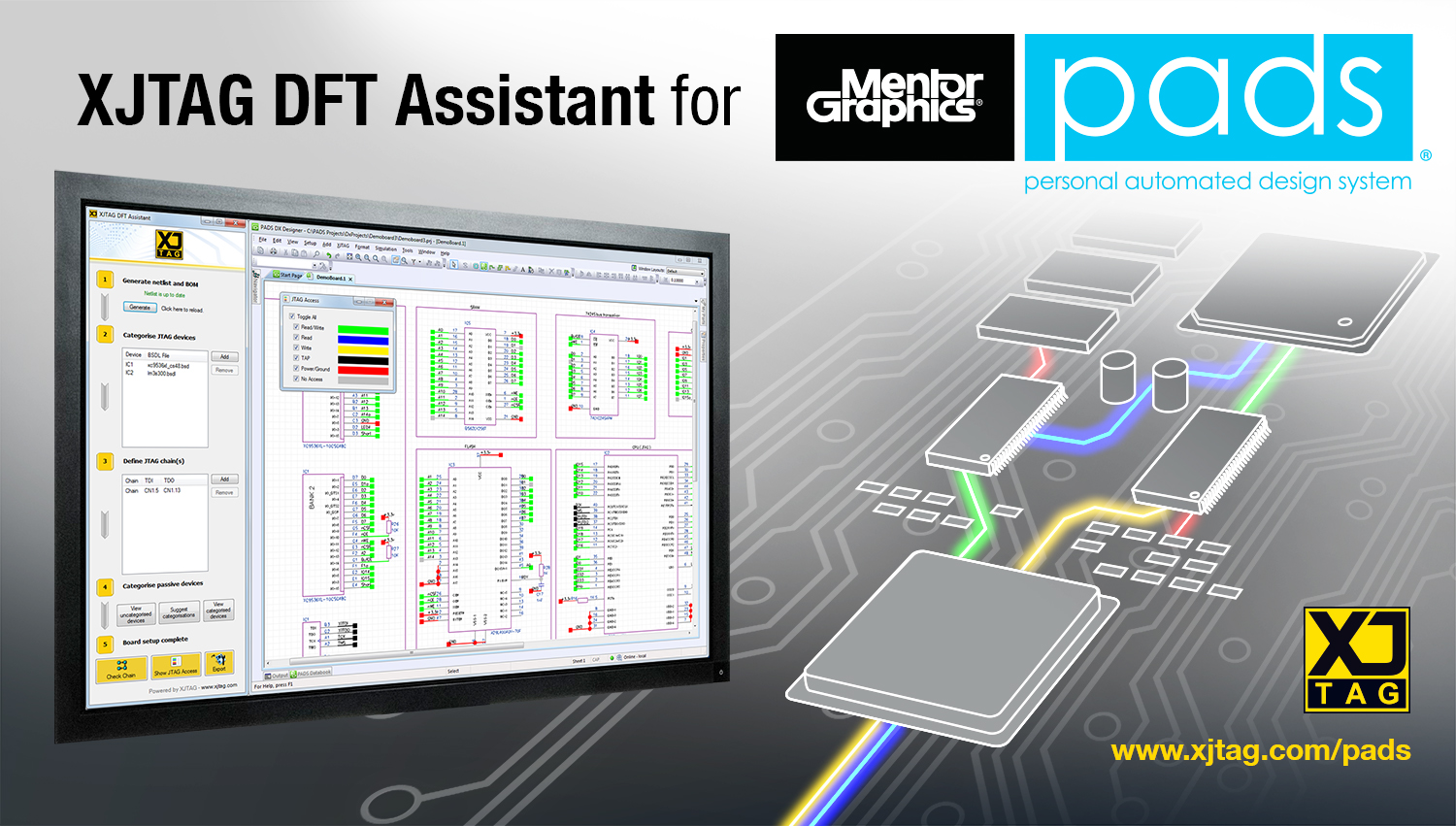

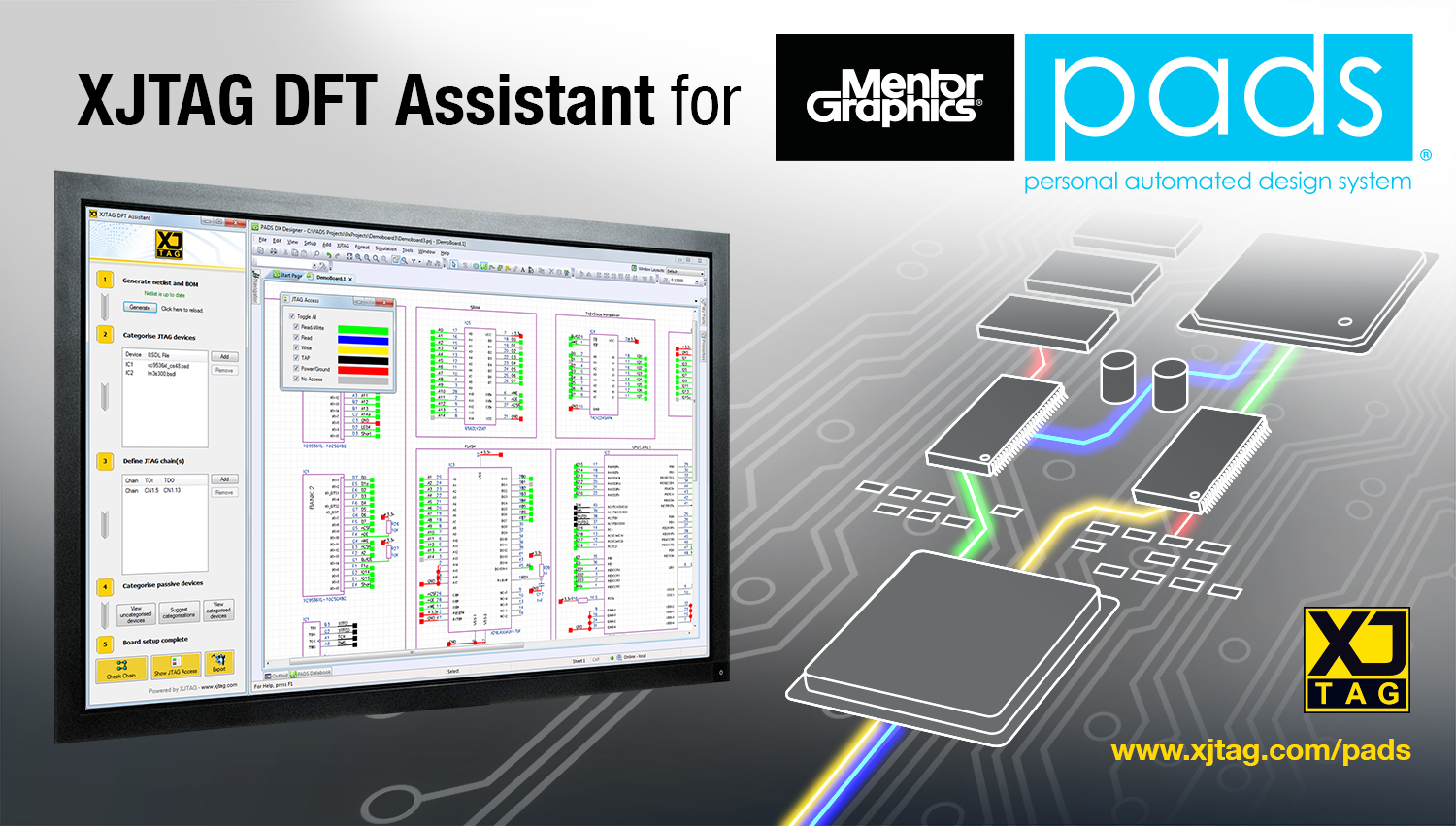

Cambridge, UK, 14. März 2017 – Von XJTAG® entwickelt, wird die kostenlose Software für PADS® Schematic-Design die Test- und Debugging-Funktionen der schematischen Capture- und PCB-Designumgebung deutlich erweitern.

Leiterplatten werden zunehmend dicht bestückt und der Zugang zu den Pins unter vielen Packages wie bspw. Ball Grid Array (BGA) ist praktisch unmöglich. JTAG wurde entworfen, um das Zugangsproblem zu beheben und somit ist es von entscheidender Bedeutung, die JTAG-Kette bereits direkt in der Designphase korrekt zu implementieren. Das Versäumnis, Designfehler frühzeitig zu erkennen und zu beheben, kann zu einem Re-Spin und einer kostspieligen Verzögerung bei einem Projekt führen. Der XJTAG-DFT- Assistant unterstützt die korrekte JTAG-Kettenkonnektivität durch die vollständige Integration mit der PADS-Schematic-Capture-Umgebung.

„PADS-Produkte beinhalten ab sofort den XJTAG-DFT-Assistant, der Ingenieuren eine kostenlose, einfach zu bedienende Benutzeroberfläche zur Verfügung stellt, um zu überprüfen, ob JTAG-Ketten in der schematischen Capture-Phase korrekt verbunden und abgeschlossen sind, lange bevor die Leiterplatte hergestellt wird“, sagt Jim Martens, Produktmarketingmanager bei der PADS Solutions Group. „Durch frühzeitige Erkennung und Korrektur dieser Fehler sparen Unternehmen sowohl Zeit als auch Geld. Die Software ist kostenlos für PADS-Nutzer der Versionen VX.2.1 oder höher und kann auf old.xjtag.com/pads heruntergeladen werden.“

Der XJTAG-DFT-Assistant besteht aus zwei Kernelementen: dem XJTAG-Chain-Checker und dem XJTAG-Access-Viewer.

Der XJTAG-Chain-Checker identifiziert gängige Fehler in einer JTAG-Scan-Kette, wie z. B. falsch verbundene Test-Access-Ports (TAPs). Ein einzelner Verbindungsfehler würde eine gesamte Scankette daran hindern, zu arbeiten. Zudem identifiziert das Tool Verbindungsfehler und meldet sie dem Entwickler während des Designprozesses. Falsch abgeschlossene TAPs werden ebenfalls identifiziert.

Der XJTAG-Access-Viewer blendet den Umfang des Boundary-Scan-Zugriffs auf dem Schaltplan ein, so dass der Anwender sofort sehen kann, welche Komponenten mit Boundary-Scan zugänglich sind und an welchen Stellen die Testabdeckung weiter ausgebaut werden könnte. Ingenieure können die Netze einzeln markieren, um Lese-/Schreibzugriff, Power/Ground anzuzeigen und auch Netze, die keinen JTAG-Zugang haben, auf dem Schaltplan sichtbar machen.

Während der erste Prototyp hergestellt wird, ermöglicht der XJTAG-DFT-Assistant den Ingenieuren, ein vorläufiges XJTAG-Projekt aus der PADS-Schematic-Capture-Umgebung in die XJTAG-Entwicklungssoftware zu exportieren, wo zusätzliche Tests entwickelt werden können. Besagte Tests können dann verwendet werden, um die tatsächliche Hardware zu testen, sobald diese verfügbar ist. Dies bietet Elektroingenieuren weltweit wichtiges neues Potential.

Über Mentor Graphics (www.mentor.com)

Mentor Graphics Corporation (NASDAQ: MENT) ist Weltmarktführer im Bereich Software- und Hardwarelösungen für die Entwicklung elektronischer Schaltungen. Zu Mentors Portfolio gehören Produkte, Beratungs- und Supportdienstleistungen, auf die die weltweit erfolgreichsten Elektronik- und Halbleiterhersteller vertrauen und dies mit der Verleihung zahlreicher Auszeichnungen an Mentor zum Ausdruck gebracht haben. Das 1981 gegründete Unternehmen erzielte in den zurückliegenden zwölf Monaten einen Gesamtumsatz von schätzungsweise 1,28 Mrd. US-Dollar. Der Hauptsitz von Mentor Corporate befindet sich in den USA, 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777. Weitere Informationen finden Sie unter: www.mentor.com

Über XJTAG (old.xjtag.com)

XJTAG ist ein weltweit führender Anbieter von Software- und Hardware-Tools für JTAG-Boundary-Scan. Das Unternehmen konzentriert sich auf innovative Produktentwicklung und qualitativ hochwertigen technischen Support. XJTAG-Produkte verwenden IEEE Std.1149.x (JTAG-Boundary-Scan), um Ingenieuren das Debuggen, Testen und Programmieren von elektronischen Schaltungen schnell und einfach zu ermöglichen. Die Design-, Entwicklungs- und Fertigungsprozesse können so erheblich verkürzt werden. Weitere Informationen über das Unternehmen, Produkte und Dienstleistungen finden Sie unter old.xjtag.com.

Bilder (klicken Sie für hohe Auflösung auf die Vorschau)

XJTAG® DFT Assistant für Mentor Graphics® PADS®